| RINRIA                                                                |                                                                            |

|-----------------------------------------------------------------------|----------------------------------------------------------------------------|

| <u>Syllabus</u>                                                       | Translating Pure Esterel v5 into<br>behavioral VHDL                        |

| Introduction<br>Esterel<br>VHDL<br>Issues<br>Translation<br>Solutions |                                                                            |

| Conclusion                                                            | Synchron'02                                                                |

|                                                                       | INRIA Sophia-Antipolis - TICK                                              |

|                                                                       | Bertrand Blanc                                                             |

|                                                                       | ENSMP - CMA Sophia-Antipolis, France © 2002<br>Bertrand.Blanc@cma.inria.fr |

| RINRI                                                                                                                                                                                                                                                                                   | A Summary of issues                                                                                                                                                                                                                                                                                                                                                                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

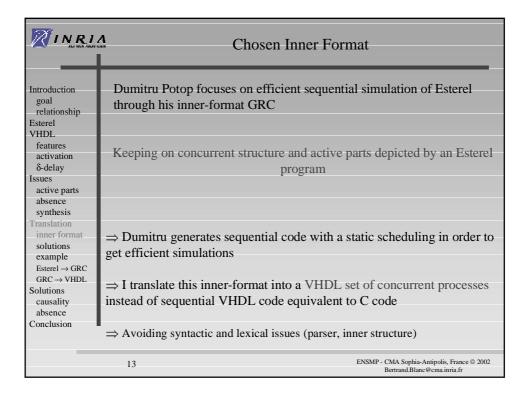

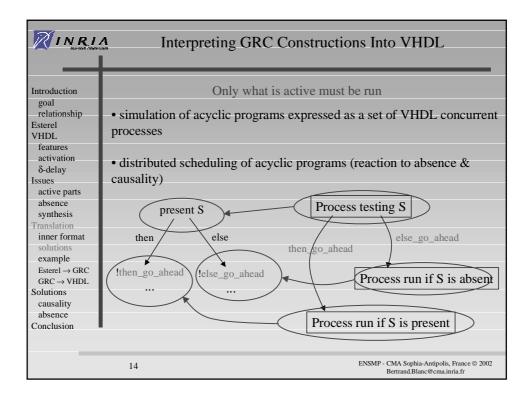

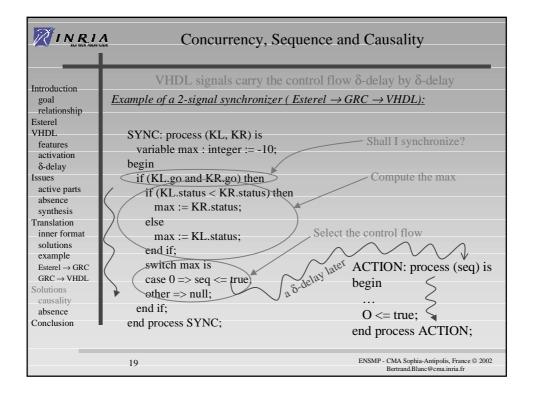

| Introduction<br>goal<br>relationship<br>Esterel<br>VHDL<br>features<br>activation<br>&-delay<br>Issues<br>active parts<br>absence<br>synthesis<br>Translation<br>inner format<br>solutions<br>example<br>Esterel → GRC<br>GRC → VHDL<br>Solutions<br>causality<br>absence<br>Conclusion | <ul> <li>Esterel → VHDL:         <ul> <li>→ translating Esterel causality (actions occur before one another) into VHDL δ-delays</li> <li>→ translating the reaction to absence algorithm into VHDL statements</li> <li>→ identifying the target subset of VHDL</li> </ul> </li> <li>VHDL → Esterel: aims at writing specifications in VHDL with the Esterel's semantics</li> </ul> |

|                                                                                                                                                                                                                                                                                         | 12 ENSMP - CMA Sophia-Antipolis, France © 2002<br>Bertrand.Blanc@cma.inria.fr                                                                                                                                                                                                                                                                                                      |

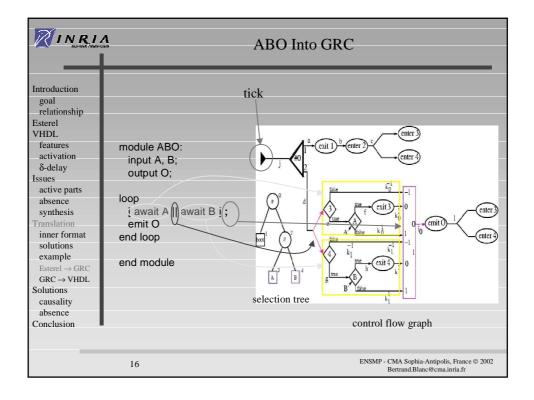

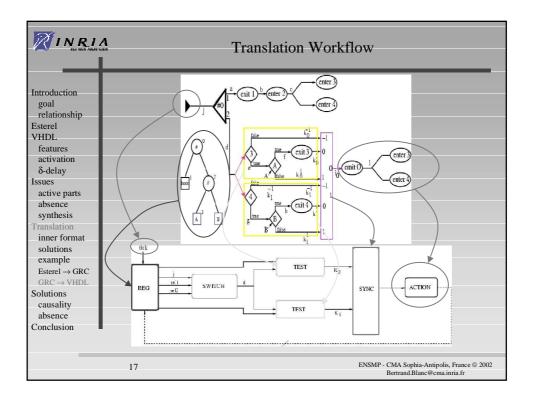

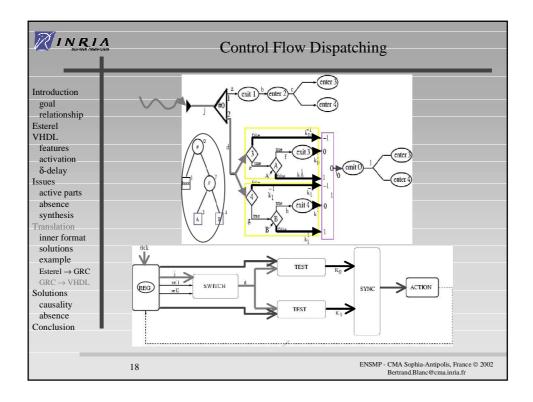

| <b>RINRI</b>                                                                                                                                                                                                                                                                                                            | A Simple Esterel Program                                                                                     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| Introduction<br>goal<br>relationship<br>Esterel<br>VHDL<br>features<br>activation<br>$\delta$ -delay<br>Issues<br>active parts<br>absence<br>synthesis<br>Translation<br>inner format<br>solutions<br>example<br>Esterel $\rightarrow$ GRC<br>GRC $\rightarrow$ VHDL<br>Solutions<br>causality<br>absence<br>Conclusion | module ABO:<br>input A, B;<br>output O;<br>loop<br>[ await A    await B ] ; emit O<br>end loop<br>end module |

|                                                                                                                                                                                                                                                                                                                         | 15 ENSMP - CMA Sophia-Antipolis, France © 2002<br>Bertrand.Blanc@cma.inria.fr                                |

| RINRIA                                                                                                                                                                                                                                                                                                                  | R                                                                                                                                                                                   | eaction to Absence                                                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

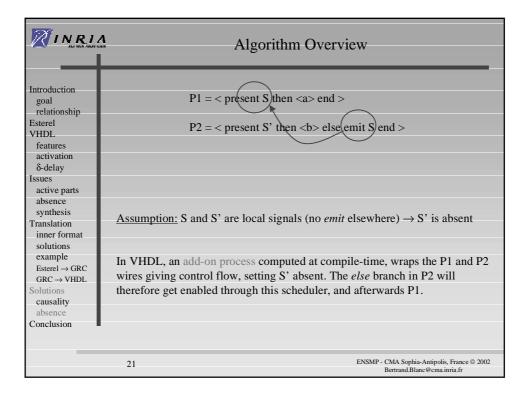

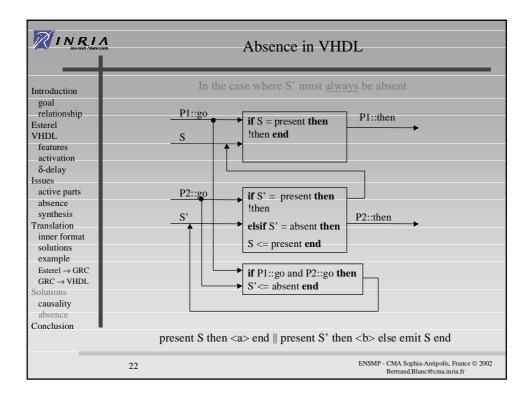

| Introduction<br>goal<br>relationship<br>Esterel<br>VHDL<br>features<br>activation<br>$\delta$ -delay<br>Issues<br>active parts<br>absence<br>synthesis<br>Translation<br>inner format<br>solutions<br>example<br>Esterel $\rightarrow$ GRC<br>GRC $\rightarrow$ VHDL<br>Solutions<br>causality<br>absence<br>Conclusion | P1<br>• S' present ⇒ nothing to de<br>environment giving the com<br>• S' absent ⇒ work to be de<br>programs, P2 must be activa<br>→ an extra process tha<br>generated at compile-ti | t enforces this condition (S' is set absent) must be                       |

|                                                                                                                                                                                                                                                                                                                         | 20                                                                                                                                                                                  | ENSMP - CMA Sophia-Antipolis, France © 2002<br>Bertrand.Blanc@cma.inria.fr |

| <b>ZINRI</b>                                                                                                                                                                                                                                                                                                            | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Introduction<br>goal<br>relationship<br>Esterel<br>VHDL<br>features<br>activation<br>$\delta$ -delay<br>Issues<br>active parts<br>absence<br>synthesis<br>Translation<br>inner format<br>solutions<br>example<br>Esterel $\rightarrow$ GRC<br>GRC $\rightarrow$ VHDL<br>Solutions<br>causality<br>absence<br>Conclusion | <ul> <li>Model of computation of pure Esterel v5 into VHDL sticking to Esterel semantics</li> <li>Usage of GRC simulation-oriented intermediate format</li> <li>Respect causality through activating conditions</li> <li>Foundations of reaction to absence through a distributed algorithm</li> <li>Generate RTL code from the behavioral VHDL and the sorted equations VHDL:</li> <li>→ compare the number of wires and registers</li> </ul> |

|                                                                                                                                                                                                                                                                                                                         | 23 ENSMP - CMA Sophia-Antipolis, France © 2002<br>Bertrand.Blanc@cma.inria.fr                                                                                                                                                                                                                                                                                                                                                                  |

| RINRIA                                                                                                                                                                                                | Future Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Introduction<br>goal<br>relationship<br>Esterel<br>VHDL<br>features<br>activation<br>&-delay<br>Issues<br>active parts<br>absence<br>synthesis<br>Translation<br>inner format<br>solutions<br>example | <ul> <li>Generalize the VHDL algorithm implementing reaction to absence to the case of several simultaneous emitters</li> <li>Find a better algorithm to encode the states (<i>selection tree</i>) used in VHDL         <ul> <li>reduce redundant registers: Dumitru already did it for sequence efficient code.</li> </ul> </li> <li>Test the scalability of the generated descriptions         <ul> <li>Identify the subset of VHDL and a methodology to implement in VHDL the Esterel semantics</li> </ul> </li> </ul> |  |

| $Esterel \rightarrow GRC$<br>$GRC \rightarrow VHDL$<br>Solutions<br>causality<br>absence<br>Conclusion                                                                                                | BUT: Attend Ph.D. program at Ecole des Mines de Paris to work on Hybrid Systems.                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 24 ENSMP - CMA Sophia-Antipolis, France © 2002<br>Bertrand.Blanc@cma.inria.fr                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |